A miniaturized radar chip, developed by researchers at Science Tokyo, advances Integrated Sensing and Communication for Beyond 5G and 6G systems. Measuring just 0.24 mm2 and consuming only 9.8 mW, the compact, low-power device generates high-speed, highly linear chirps by embedding linearization directly into the hardware, overcoming traditional speed-versus-accuracy limits and enabling precise sensing for edge and Internet-of-Things devices.

A Self-Linearized FMCW Chirp Synthesizer for 6G Integrated Sensing and Communication

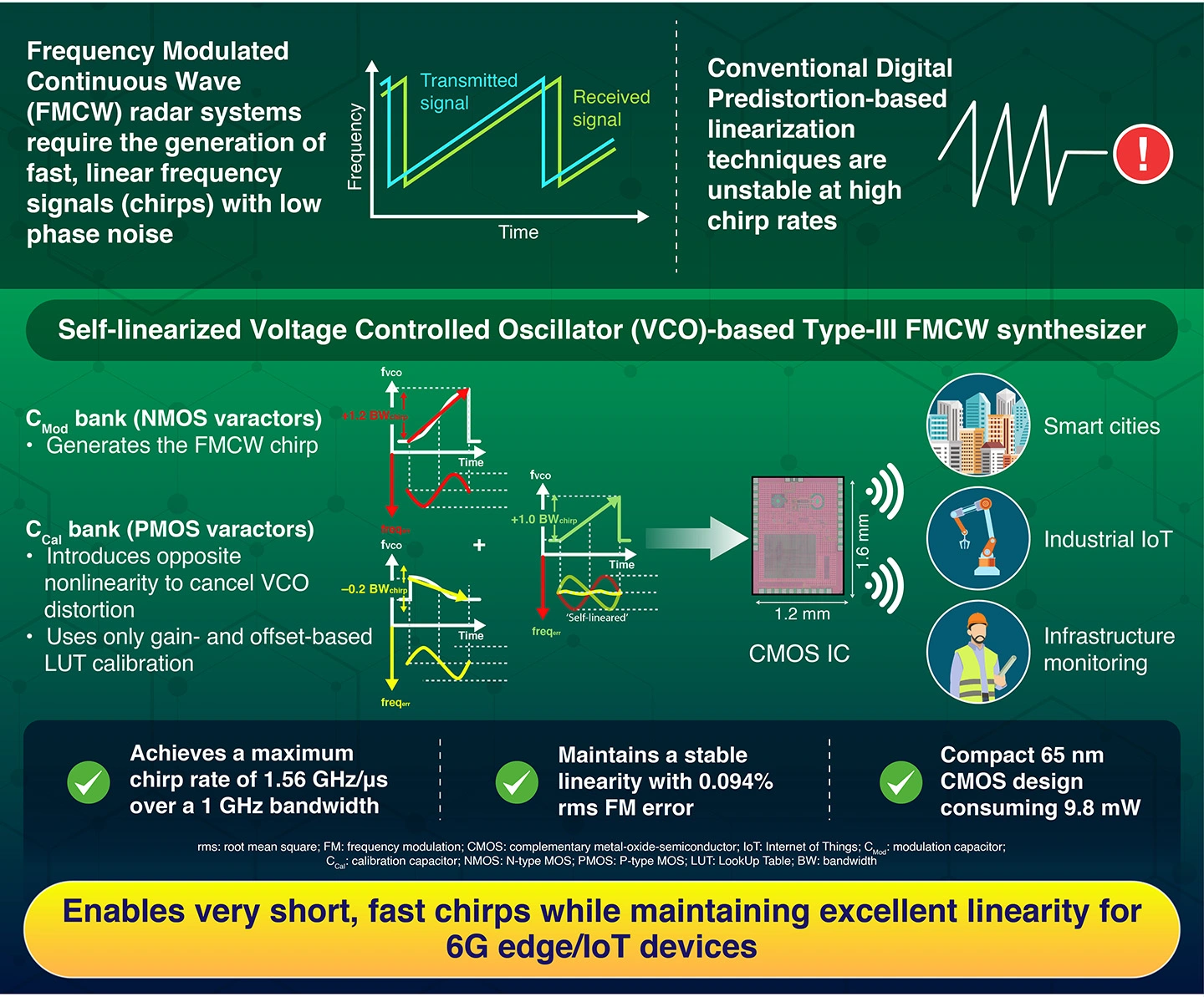

Integrated Sensing and Communication (ISAC), which combines wireless data transmission with radar-like environmental sensing in a single system, is widely considered an important direction for Beyond 5G and 6G research. Its deployment in the new Frequency Range 3 band, ranging from 7.125 to 24.25 GHz, is expected to support applications such as smart cities, industrial Internet-of-Things (IoT), and large-scale connected devices.

One of the key hardware requirements for such systems is the ability to measure distance and motion with high precision. This can be achieved using the Frequency-Modulated Continuous Wave (FMCW) radar, which transmits signals whose frequency changes linearly over time, known as chirps, and analyzes the difference between transmitted and reflected waves to determine a target's range and velocity. The performance of this radar depends on generating chirp signals that are both very fast (high chirp rate) and highly linear.

A research team led by Professor Kenichi Okada from the Department of Electrical and Electronic Engineering, School of Engineering, Institute of Science Tokyo (Science Tokyo), Japan, has developed a compact, low-power FMCW radar signal generator chip that operates at 9.7 GHz using a Type-III synthesizer architecture. The core circuit occupies just 0.24 mm2 and consumes approximately 9.8 mW during operation, making it suitable for integration into edge and IoT devices. The work is scheduled to be presented at the 2026 IEEE International Solid-State Circuits Conference (ISSCC), to be held in San Francisco, USA, from February 15-19, 2026.

"We proposed a new circuit architecture that generates chirp signals, satisfying both the high chirp rate required for fast-moving target detection and the wide bandwidth required for high-resolution ranging, as well as the high linearity required for high-accuracy measurement in FMCW radar, by self-compensating the nonlinearity of the Voltage-Controlled Oscillator (VCO) within the circuit," says Okada.

Conventional FMCW signal generators often rely on Digital Predistortion (DPD) to correct oscillator nonlinearity by applying an inverse response to the input signal. Here, the chirp is approximated using a piecewise linear Lookup Table (LUT) with 64 segments, corresponding to 6-bit resolution. Each segment provides a small correction to improve the linearity of the frequency sweep, and the correction coefficients are updated based on measured phase error.

At high chirp rates, however, the chirp duration becomes very short. This reduces the number of phase samples available for each segment, which can make the coefficient updates unstable and degrade chirp linearity. Reducing the LUT depth, for example, from 64 segments to 16, increases the number of samples per segment and improves stability, but at the cost of larger residual frequency error after linearization.

The researchers addressed this limitation by embedding the linearization function directly into the oscillator hardware. This architecture includes a ramp tracker that generates the chirp while reducing gain error, and a VCO nonlinearity calibration block that compensates residual distortion. The main modulation elements and the calibration elements use NMOS and PMOS varactors with opposite nonlinear characteristics, allowing their distortions to cancel each other when properly tuned. This approach requires calibrating only two parameters, gain and offset, using two small LUTs. As a result, digital overhead is reduced and stable operation can be maintained even at very high chirp rates.

The researchers fabricated a prototype chip using a 65-nanometer CMOS process and demonstrated it to generate chirp signals at 9.7 GHz with a sweeping bandwidth of 1 GHz. "It achieves the shortest chirp duration of 0.57 μs, a 40 ns retrace, and a 1562.8 MHz/μs chirp rate, delivering a 1 GHz bandwidth with a 0.094% rms FM error," says Okada.

This design successfully overcomes the longstanding trade-off between chirp speed and signal linearity for FMCW radar. It marks an important step toward the practical deployment of ISAC into a wide range of edge and IoT devices, bringing us closer to a seamlessly connected 6G society.

These research results were obtained from the commissioned research (No. JPJ012368C00801) by National Institute of Information and Communications Technology (NICT), Japan.

Reference

- Authors:

- Daxu Zhang, Yuncheng Zhang, Zezheng Liu, Yuang Xiong, Michele Rossoni, Wenqian Wang, Ashbir Aviat Fadila, Duo Li, Minzhe Tang, Dongfan Xu, Carrel de Gomez, Dingxin Xu, Kazuaki Kunihiro, Hiroyuki Sakai, and Kenichi Okada*

*Corresponding author

- Title:

- A 9.7 GHz Self-Linearized-VCO-Based FMCW Chirp Generator Achieving 1.56 GHz/μs Slope and 0.57 μs Duration with 0.094% rms Frequency Error

- Journal:

- Proceedings of the 2026 IEEE International Solid-State Circuits Conference (ISSCC)

- Affiliations:

- Department of Electrical and Electronic Engineering, Institute of Science Tokyo, Japan